# **RC7316**

# Three-State ATE Pin Electronics Driver

#### **Features**

- High output slew rate (3.2 V/ns) typical driving coax

- Wide output voltage range (-2.0V to +7V), and up to 9 Vp-p swings

- Three-state/high impedance output

- High repetition rate (550 MHz for ECL swings)

- Low output offset (40 mV typical) and output offset drift (0.1 mV/°C typical

- Low leakage (10 nA typical) and low output capacitance (3.0 pF typical) in high impedance inhibit mode

- 100 mA typical dynamic current drive capability

- High speed differential inputs with wide common mode range for ease of interface to ECL as well as TTL and CMOS levels

- Output short circuit protection (Safe Operating Area protection with current limiting and thermal shutdown)

- · Available in 16 Lead Hybrid Flatpack

- RC7316TEL is pin-for-pin compatible with AD1321, AD1322, and AD1324

## **Applications**

- · ATE pin electronics driver

- Precision waveform generator

- · Level translator

- Differential line receiver

- · General purpose driver

- · Laser driver

- · CRT preamplifier

#### **Description**

The RC7316 Pin Electronics Driver is designed for use in ultra high speed ATE systems which require pin drivers with three state capability and high slew rates. The RC7316 has the ability to drive a  $50\Omega$  transmission line of up to 2 feet in length with a slew rate of 3.2 V/ns and repetition rate of over 550 MHz for ECL output levels. These features, combined with a maximum output swing of 9.5 Vp-p over the range of -3.0V to +7V, provide this circuit with the ability to test TTL, CMOS, ECL and GaAs devices. The high and low limits of the output swing are set through the program pins VH and VL, respectively. The transfer characteristic from the program pins to the output pin is unity gain with very low offset drift. The VH and VL inputs have been buffered to operate with low bias currents (1  $\mu$ A typical) allowing direct coupling to the output of a DAC.

When the RC7316 is used on an I/O pin, it may be forced into the high impedance state through the INH+ and INH-differential inputs. In the high impedance state, excellent isolation is provided between the output of the disabled driver and the pin by virtue of low driver output capacitance (3.0 pF typical) and low output leakage (10 nA typical).

The RC7316 is provided with high speed differential ECL inputs for ease of interface with the differential ECL outputs of a timing generator. The inputs have a voltage range of -2V to +6V, so that if required, an input may be driven by TTL or CMOS devices provided that the other input is fed to the appropriate threshold value.

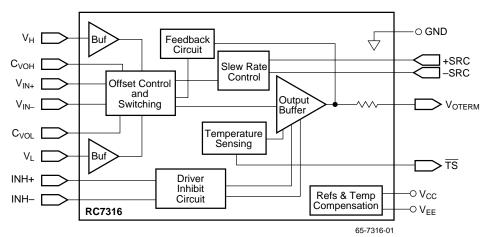

## **Block Diagram**

## **Description** (continued)

The pin driver is available in  $50\Omega$  series terminated RC7316 (TEL) configurations. The RC7316TEL is pin-for-pin compatible with Analog Devices' AD1321, AD1322 and AD1324 drivers.

The RC7316 is implemented using Raytheon Electronic's high frequency BiCMOS process.

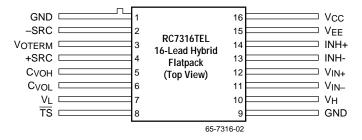

## **Pin Assignments**

# **Pin Descriptions**

| Pin Name   | Pin Number | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CVOL, CVOH | 6, 5       | Bypass capacitor for VOH and VOL respectively. Pins CVOL and CVOH should be bypassed to the ground plane with a 1,000 pF chip capacitor placed as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND        | 1, 9       | Chip ground. Should be connected to the printed circuit board's ground plane at the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INH+, INH- | 13, 14     | Differential digital inputs. When INH is true (i.e. INH+ > INH-) the driver is forced into the high impedance state. Although these inputs are normally driven by ECL signals, they have a wide enough common mode range that any one of the inputs may be driven by a TTL or CMOS signal provided that the other input is tied to the appropriate threshold voltage.                                                                                                                                                                                                                                              |

| +SRC       | 4          | Slew rate control for the positive edge. Slew rate of the positive edge changes as the control voltage is changed from -2.0V to +2.0V. +SRC can also be programmed with a current DAC or set to a fixed value using a resistor. Optionally, pin 4 can be NC. (No Connection)                                                                                                                                                                                                                                                                                                                                       |

| -SRC       | 2          | Slew Rate Control for the negative edge. Slew rate of the negative edge changes as the control voltage is changed from -2.0V to +2.0VSRC can also be programmed with a current DAC or set to a fixed value using a resistor. Optionally, pin 2 can be NC. (No Connection)                                                                                                                                                                                                                                                                                                                                          |

| TS         | 8          | Active low output notifies thermal shutdown has occurred. In the event of a short circuit or other fault that causes the die temperature to become excessively large, the thermal shutdown will kick in at a die temperature between 115°C and 160°C. If the fault persists, the device will toggle back and forth between shutdown and normal operation at a frequency in the tens of Hertz. TS is an open collector output capable of driving two standard TTL loads. The TS pins of several drivers may be wire-ORed together and input to a latch to indicate an alarm condition. Optionally, pin 8 can be NC. |

| Vcc        | 16         | Quiet positive supply. The nominal value is 10V $\pm 3\%$ . For output high voltage levels (VOH) greater than the nominal value of $\pm 7$ V, VCC should be raised 3V above the maximum value of VOH. Whenever VEE is lowered to provide margin at the output low level, VCC should also be lowered by the same amount. VCC should be bypassed to ground with a 10,000 pF chip capacitor placed as close to the pins as possible.                                                                                                                                                                                  |

# Pin Descriptions (continued)

| Pin Name   | Pin Number | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Vcco       |            | Positive supply for the RC7316 output stage. This supply is brought out separately to minimize the supply noise generated when the output switches. VCCO should be bypassed to the ground plane with a 10,000 pF chip capacitor placed as close to the pin as possible and then immediately connected to VCC.                                                                                                                                                                                       |  |

| VEE        | 15         | Quiet negative supply. The nominal value is -5.2V $\pm$ 5%. For output low voltage levels (V <sub>OL</sub> ) less than the nominal value of -2.5V, V <sub>EE</sub> should be lowered 3V below the minimum value of V <sub>OL</sub> . Whenever V <sub>CC</sub> is raised to provide margin at the output high level, V <sub>EE</sub> should also be raised by the same amount. V <sub>EE</sub> should be bypassed to ground with a 10,000 pF chip capacitor placed as close to the pins as possible. |  |

| VEEO       |            | Negative supply for the RC7316 output stage. This supply is brought out separately to minimize the supply noise generated when the output switches. VEEO should be bypassed to the ground plane with a 10,000 pF chip capacitor placed as close to the pin as possible and then immediately connected to VEE.                                                                                                                                                                                       |  |

| VH         | 10         | Analog program input that sets the output high level (VOH) The transfer characteristic from VH to VOH is nominally unity gain.                                                                                                                                                                                                                                                                                                                                                                      |  |

| VIN+, VIN- | 11,12      | Differential digital inputs. The output will toggle between the two levels dictated by V <sub>H</sub> and V <sub>L</sub> as the differential signal is switched. Although these inputs are normally driven by ECL signals, they have a wide enough common mode range that any one of the inputs may be driven by a TTL or CMOS signal provided that the other input is tied to the appropriate threshold voltage.                                                                                   |  |

| VL         | 7          | Analog program input that sets the output low level (VOL). The transfer characteristic from VLto VOL is nominally unity gain.                                                                                                                                                                                                                                                                                                                                                                       |  |

| Vo         |            | Driver output on RC7316. The output impedance is $10\Omega \pm 2\Omega$ . The output is usually back terminated in the characteristic impedance of the transmission line it drives. For a $50\Omega$ line, a $40\Omega \pm 1\%$ resistor should be placed externally as close to the output pin as possible to minimize reflections and ringing. The resistor should also be able to dissipate $0.8\Omega$ to sustain the short circuit current of the output.                                      |  |

# **Absolute Maximum Ratings<sup>1</sup>**

| Parameter                                                                               | Min.   | Max.       | Units |

|-----------------------------------------------------------------------------------------|--------|------------|-------|

| Positive power supply, VCC                                                              |        | 13         | V     |

| Negative power supply, VEE                                                              | -8.2   |            | V     |

| Difference between VCC and VEE                                                          |        | 16         | V     |

| Input voltage at V <sub>IN+</sub> , V <sub>IN-</sub> , INH+, INH-                       | VCC-12 | VEE+12     | V     |

| Input Voltage at VH, VL                                                                 | VCC-13 | VEE+13     | V     |

| Differential input voltage,   VIN+-VIN-  ,   VINH+ - VINH-                              |        | 6          | V     |

| Difference between V <sub>H</sub> & V <sub>L</sub> ( V <sub>H</sub> - V <sub>L</sub>  ) |        | 11         | V     |

| Input voltage at +SRC, -SRC                                                             | -3     | +7         | V     |

| Slew rate control current                                                               | -2.0   |            | mA    |

| Driver Output Voltage                                                                   | VCC-13 | VEE+13     | V     |

| Output voltage at TS                                                                    |        | 5          | V     |

| Duration of short-circuit to ground                                                     |        | Indefinite |       |

| Operating temperature range                                                             | 0      | 70         | °C    |

| Storage temperature range                                                               | -65    | +125       | °C    |

| Lead temperature range (Soldering 10 seconds)                                           |        | 300        | °C    |

#### Notes:

# **Recommended Operating Conditions**

| Symbol   | Parameters                                       | Min.  | Тур. | Max.  | Units |

|----------|--------------------------------------------------|-------|------|-------|-------|

| TC       | Case operating temperature                       | 0     | 25   | +70   | °C    |

| Vcc      | Positive supply voltage                          | 9.7   | 10.0 | 10.3  | °C    |

| VEE      | Negative supply voltage                          | -5.45 | -5.2 | -4.95 | V     |

| VCC-VEE  | Difference between positive and negative supply  |       | 15.2 | 15.8  | V     |

| VOH, VOL | Range for output high level and output low level | -3.0  |      | 7.0   | V     |

| Von-Vol  | Output amplitude                                 | 0.1   |      | 9.5   | V     |

| RT       | Output back-termination resistor                 |       | 41   |       |       |

4

<sup>&</sup>quot;Absolute maximum ratings" are those beyond which the safety of the device cannot be guaranteed. They are not meant to

imply that the device should be operated at these limits. If the device is subjected to the limits in the absolute maximum ratings

for extended periods, its reliability may be impaired. The tables of Electrical Characteristics provide conditions for actual

device operation.

### **DC Electrical Characteristics**

VCC = 10V  $\pm 3\%$ , VEE = -5.2V  $\pm 5\%$ , TA = 25°C (flow  $\geq 300$  Lfm) and the load is a  $50\Omega$  transmission line with 2.0 ns one-way delay, unless otherwise specified. The transmission line is back-terminated in  $50\Omega$  ( $\pm 5\%$ ) using an external resistor (RC7316).

| Symbol                                | Parameters Test Conditions                                      |                                                                           | Min. | Тур. | Max. | Units |

|---------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|------|------|------|-------|

| Diffential In                         | puts VIN+, VIN-, VINH+, VINH-                                   |                                                                           | •    |      | •    |       |

| VIN+, VIN-                            | Absolute Voltage @ Data Inputs                                  |                                                                           | -2.0 |      | +6.0 | V     |

| VINH+                                 | Absolute Voltage @ Inhibit                                      |                                                                           |      |      |      |       |

| VINH-                                 | Inputs INH+, INH-                                               |                                                                           | -2.0 |      | +5.0 | V     |

| VID                                   | Differential Input Range                                        | VIN+ - VIN-                                                               | 0.4  | ECL  | 5.0  | V     |

| VDINH                                 | Differential Inhibit Input Range                                | VINH+ - VINH                                                              | 0.4  | ECL  | 5.0  | V     |

| IIN+, IIN-                            | Input Bias Current @ Data Inputs                                | -2V ≤ VIN+, VIN- ≤ +6V                                                    | -100 | -35  |      | μΑ    |

| I <sub>INH+</sub> , I <sub>INH-</sub> | Input Bias Current @ Inhibit Inputs                             | -2V ≤ VINH+, VINH- ≤ +5V                                                  | -150 | -50  |      | μΑ    |

| Voltage Pro                           | gram Inputs VH, VL                                              |                                                                           | !    |      | •    |       |

| VH                                    | V <sub>H</sub> Range                                            | VCC = 10V; VEE = -5.2V                                                    | -2.0 |      | +7.0 | V     |

|                                       |                                                                 | VCC = 12V; VEE = -3.2V                                                    | 0    |      | +9.0 | V     |

|                                       |                                                                 | VCC = 8V; VEE = -7.2V                                                     | -4.0 |      | +5.0 | V     |

| VL                                    | V <sub>L</sub> Range                                            | VCC = 10V; VEE = -5.2V                                                    | -2.0 |      | +6.0 | V     |

|                                       |                                                                 | VCC = 12V; VEE = -3.2V                                                    | 0    |      | +8.0 | V     |

|                                       |                                                                 | VCC = 8V; VEE = -7.2V                                                     | -4.0 |      | +4.0 | V     |

| lΗ                                    | Bias Current @ VH                                               | -1V ≤ V <sub>H</sub> ≤ +7V; V <sub>L</sub> = -3.0V                        |      | 1.0  | 5.0  | μΑ    |

| IL                                    | Bias Current @ VL                                               | -3V ≤ V <sub>L</sub> ≤ +5V; V <sub>H</sub> = 6.0V                         | -5.0 | -1.0 |      | μΑ    |

| TCIH                                  | Temperature Drift in IH                                         | V <sub>H</sub> = 7.0V; 25°C ≤ T <sub>C</sub> ≤ 70°C output not switching  |      |      | 0.1  | μΑ/°C |

| TCIL                                  | Temperature Drift in IL                                         | V <sub>L</sub> = -3.0V; 25°C ≤ T <sub>C</sub> ≤ 70°C output not switching |      |      | 0.1  | μΑ/°C |

| ΔIBDC                                 | Variation in IH, ILwith power supply and DC voltage at VH or VL | -1V ≤ VH ≤ +7V<br>-2V ≤ V <sub>L</sub> ≤ + 6V                             | -1   |      | 1    | μА    |

| \/ D\\/                               | -3 dB bandwidth from V <sub>H</sub> or V <sub>L</sub> to        | -2 V ≤ V L ≤ + 0 V<br>-1 V ≤ V H ≤ +7 V;                                  | +    |      | 50   | kHz   |

| VH,LBW                                | the output                                                      | ,                                                                         |      |      | 50   | KITZ  |

| Signal Quar                           | ·                                                               | -2V ≤ V <sub>L</sub> ≤ +6V; V <sub>H</sub> -V <sub>L</sub> = 2.0V         |      |      |      |       |

|                                       | Output Voltage Bange                                            | V <sub>CC</sub> = 10V; V <sub>EE</sub> = -5.2V                            | -2.0 |      | +7.0 | V     |

| Vo                                    | Output Voltage Range                                            |                                                                           |      |      |      | '     |

|                                       |                                                                 | VCC = 12V; VEE = -3.2V<br>VCC = 8V; VEE = -7.2V                           | 0    |      | +9.0 | V     |

| \/.                                   | Amplitude                                                       |                                                                           | -4.0 |      | +5.0 | V     |

| VA                                    | Amplitude                                                       | VOH - VOL                                                                 | 0.1  | 40   | 9.5  |       |

| δVон                                  | Offset to Output High Level                                     | -1V ≤ VH ≤ +6V; VL = -2V                                                  | -100 | -40  | 100  | mV    |

| 6)/                                   | Official to Control I and Lovel                                 | $\delta VOH =  VH - VOH $                                                 | 400  | 40   | 400  | >/    |

| δVOL                                  | Offset to Output Low Level                                      | -2V ≤ VL ≤ +6V; VH = +7V                                                  | -100 | -40  | 100  | mV    |

| VTO                                   | Output Valta na Diff                                            | $\delta V_{OL} =  V_L - V_{OL} $                                          |      | 0.4  |      | \//00 |

| VTC                                   | Output Voltage Drift                                            | -1V ≤ VOH ≤ +7V                                                           | 4.0  | 0.1  | .4.0 | mV/°C |

| εG                                    | Gain Error                                                      | -2V ≤ VOL ≤ +7V                                                           | -1.0 | ±0.5 | +1.0 | %VSET |

| εL                                    | Linearity Error                                                 | 0V ≤ VOUTPUT ≤ +5V                                                        | -0.5 | ±0.2 | +0.5 | %VSET |

| 7                                     | Output long a day                                               | -2V≤ VOUTPUT ≤ +7V                                                        | -1.0 | ±0.6 | +1.0 | %VSET |

| Zout                                  | Output Impedance                                                |                                                                           |      | 50   |      |       |

## **DC Electrical Characteristics** (continued)

| Symbol             | Parameters                             | Test Cond                      | itions                 | Min. | Тур.  | Max.  | Units |

|--------------------|----------------------------------------|--------------------------------|------------------------|------|-------|-------|-------|

| IZL                | Output Leakage Current in Inhibit Mode | -2.0V ≤ V <sub>O</sub> ≤ +6.5V |                        | -200 | ±10   | +200  | nA    |

| IDC                | DC Current Drive                       |                                |                        | 50   |       |       | mA    |

| IAC                | AC Current Drive                       |                                |                        | 70   | 100   |       | mA    |

| Thermal Shi        | utdown Output (TS) (Open Collecto      | or Output)                     |                        | •    |       | •     |       |

| ICL                | DC Current Limit                       |                                |                        | 70   | 110   | 130   | mA    |

| VOL                | Output Low Level                       | IOL = 4 mA                     | 1                      |      |       | 0.5   | V     |

| TTS                | Shutdown Die Temperature               |                                |                        | 115  | 135   | 160   | °C    |

| Other              |                                        |                                |                        |      | '     |       |       |

| Vs                 | Rail to Rail Supply Voltage            | VCC - VEE                      |                        |      |       | 17    | V     |

| Vcc                | Positive Supply                        |                                |                        | +8.0 | +10.0 | +12.0 | V     |

| VEE                | Negative Supply                        |                                |                        | -7.2 | -5.2  | -3.2  | V     |

| Icc                | Positive Supply Current                |                                |                        |      | 85    |       | mA    |

| IEE                | Negative Supply Current                |                                |                        |      | 95    |       | mA    |

| PSRVO              | Output Level Power Supply              | Vcc; ΔVcc = ±2.5%              |                        |      | 40    |       | dB    |

|                    | Rejection Ratio                        | VEE; $\Delta$ VEE = ±2.5%      |                        |      | 40    |       | dB    |

| PSRV <sub>SL</sub> | Output Slew Rate Power Supply          | VH = 5V                        |                        |      |       |       |       |

|                    | Rejection Ratio @ VCC                  | and                            | $\Delta$ VCC = ±200 mV |      |       | 4     |       |

|                    | @ VEE                                  | V <sub>L</sub> = 0V            | $\Delta$ VEE = ±200 mV |      |       | 4     | %     |

#### **AC Electrical Characteristics**

VCC =  $10V \pm 3\%$ , VEE =  $-5.2V \pm 5\%$ , TA =  $25^{\circ}$ C (still air) and the load is a  $50\Omega$  transmission line with 2.0 ns one-way delay, unless otherwise specified. The transmission line is back-terminated in  $50\Omega$  ( $\pm 5\%$ ) using both internal and external termination resistance. The measurement probe is a high impedance FET probe with capacitance no greater than 3 pF and resistance no smaller than  $10 \text{ k}\Omega$ .

| Symbol           | Parameters                 | Test Conditions                                                            | Min. | Тур. | Max. | Units |

|------------------|----------------------------|----------------------------------------------------------------------------|------|------|------|-------|

| SLR              | Slew Rate                  | VH - VL = 5V; Measured between 20% and 80% points. With probe only as load | 3.0  | 3.5  |      | V/ns  |

|                  |                            | With probe and transmission                                                | 0.0  | 0.0  |      | 77110 |

|                  |                            | line                                                                       | 2.7  | 3.2  |      | V/ns  |

| +SRC             | Positive SLR Control + SRC |                                                                            |      |      |      |       |

|                  | Control Voltage Range      | VH = +5V, VL = 0V                                                          | -2.0 |      | +2.0 | V     |

|                  | Slew Rate Change           |                                                                            | 0.5  |      | +3.5 | V/ns  |

| -SRC             | Negative SLR Control –SRC  |                                                                            |      |      |      |       |

|                  | Control Voltage Range      | V <sub>H</sub> = +5V, V <sub>L</sub> = 0V                                  | -2.0 |      | +2.0 | V     |

|                  | Slew Rate Change           |                                                                            | 0.5  |      | +3.5 | V/ns  |

| t <sub>R</sub> , | Rise Time, and             | C <sub>L</sub> = 5.0 pF                                                    |      |      |      |       |

| tF               | Fall Time                  | VA = 0.8V (20% to 80%)                                                     |      | 0.5  | 0.8  | ns    |

|                  |                            | V <sub>A</sub> = 3V (10% to 90%)                                           |      | 1.0  | 1.4  | ns    |

|                  |                            | V <sub>A</sub> = 5V (10% to 90%)                                           |      | 1.4  | 1.8  | ns    |

6

# AC Electrical Characteristics (continued)

| Symbol             | Parameters                                             | Test Conditions                                                                                        | Min. | Тур.                              | Max. | Units |

|--------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------------------------|------|-------|

| f                  | Toggle Rate                                            | Amplitude = 0.8 Vp-p                                                                                   | 500  | 550                               |      | MHz   |

|                    | (Probe only)                                           | Amplitude = 3.0 Vp-p                                                                                   | 275  | 300                               |      | MHz   |

|                    |                                                        | Amplitude = 5.0 Vp-p                                                                                   | 200  | 220                               |      | MHz   |

| tPHL               | High to Low Propagation Delay                          | f = 10 MHz; V <sub>OH</sub> = +0.4V;                                                                   |      |                                   |      |       |

|                    |                                                        | VOL = -0.4V                                                                                            |      | 1.7                               | 2.0  | ns    |

| Δtp                | Propagation Delay Match                                | tplh - tphl                                                                                            |      | 30                                | 100  | ps    |

| tPTC               | Propagation Delay Temperature<br>Coefficient           |                                                                                                        |      | 2                                 |      | ps/°C |

| tPW <sub>min</sub> | Minimum Pulse Width                                    | VH - VL - 2.0V; pulsewidth at which amplitude drops by 50 mV, measured between 50% points. CL = 5.0 pF |      | 1.1                               |      | ns    |

| ΔtpPW              | Propagation Delay Variation with Pulse Width           | 2 ns < PW < 98 ns;<br>f = 10 MHz; V <sub>OH</sub> = +0.4V;<br>V <sub>OL</sub> = -0.4V                  |      | 40                                | 150  | ps    |

| tps                | Preshoot                                               | 0.5V < VA < 5.0V                                                                                       |      | 15mV<br>+ 3%<br>of V <sub>A</sub> |      | ns    |

| tos                | Overshoot                                              | 0.5V < VA < 5.0V                                                                                       |      | 50mV<br>+ 4%<br>of V <sub>A</sub> |      | ns    |

| ts                 | Output Settling Time                                   | VA = 5V;                                                                                               |      |                                   |      |       |

|                    |                                                        | To within 3% of VA                                                                                     |      | 5.0                               |      | ns    |

|                    |                                                        | To within 1% of VA                                                                                     |      | 12.0                              |      | ns    |

| tPHZ               | Propagation Delay from Logic<br>High to Inhibit Mode   | V <sub>OH</sub> = 1V; V <sub>OL</sub> = -1V<br>Load = 100Ω                                             |      | 1.5                               | 2.0  | ns    |

| tPLZ               | Propagation Delay from Logic<br>Low to Inhibit Mode    | to 2.5V; Propagation delay is<br>measured to the point at which<br>voltage has changed by 200          |      | 2.0                               | 2.5  | ns    |

| tPZH               | Propagation Delay from Inhibit<br>Mode from Logic High | mV.                                                                                                    |      | 2.2                               | 2.5  | ns    |

| tPZL               | Propagation Delay from Inhibit<br>Mode to Logic Low    |                                                                                                        |      | 2.2                               | 2.5  | ns    |

| Cz                 | Output Capacitance in Inhibit Mode                     |                                                                                                        |      | 3.0                               |      | pf    |

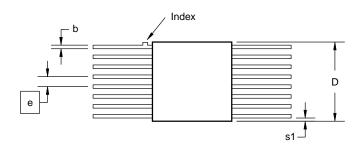

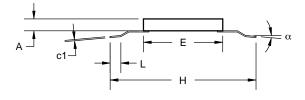

### **Mechanical Dimensions**

## 16-Lead Hybrid Flatpack

| Symbol | Inches   |      | Millim   | Notes |       |

|--------|----------|------|----------|-------|-------|

| Symbol | Min.     | Max. | Min.     | Max.  | Notes |

| A      | .072     | .088 | 1.83     | 2.24  |       |

| b      | .013     | .017 | 0.33     | 0.43  |       |

| c1     | .007     | .010 | 0.18     | .15   |       |

| D/E    | .442     | .458 | 11.23    | 11.63 |       |

| е      | .050 BSC |      | 1.27 BSC |       |       |

| Н      | .675     | .685 | 17.15    | 17.40 |       |

| L      | .050     | .065 | 1.40     | 1.65  |       |

| s1     | .005     | -    | .13      | -     |       |

| α      | 0°       | 5°   | 0°       | 5°    |       |

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Gold plate 80  $\mu^{\text{\tiny "}}$  min. nickel over 80  $\mu^{\text{\tiny "}}$  min. nickel.

- 3. Leads 1 and 9 connect to ground, seal ring, and heat sink pad.

## **Ordering Information**

| Part Number | Package | Operating Temperature Range |

|-------------|---------|-----------------------------|

| RC7316TEL   | EL      | 0°C to +70°C                |

#### Notes:

TEL = 16 Lead Hybrid Flatpack,  $50\Omega$  termination (AD1322 pinout)

The information contained in this data sheet has been carefully compiled; however, it shall not by implication or otherwise become part of the terms and conditions of any subsequent sale. Raytheon's liability shall be determined solely by its standard terms and conditions of sale. No representation as to application or use or that the circuits are either licensed or free from patent infringement is intended or implied. Raytheon reserves the right to change the circuitry and any other data at any time without notice and assumes no liability for errors.

#### LIFE SUPPORT POLICY:

Raytheon's products are not designed for use in life support applications, wherein a failure or malfunction of the component can reasonably be expected to result in personal injury. The user of Raytheon components in life support applications assumes all risk of such use and indemnifies Raytheon Company against all damages.

Raytheon Electronics Semiconductor Division 350 Ellis Street Mountain View, CA 94043 415.968.9211 FAX 415.966.7742